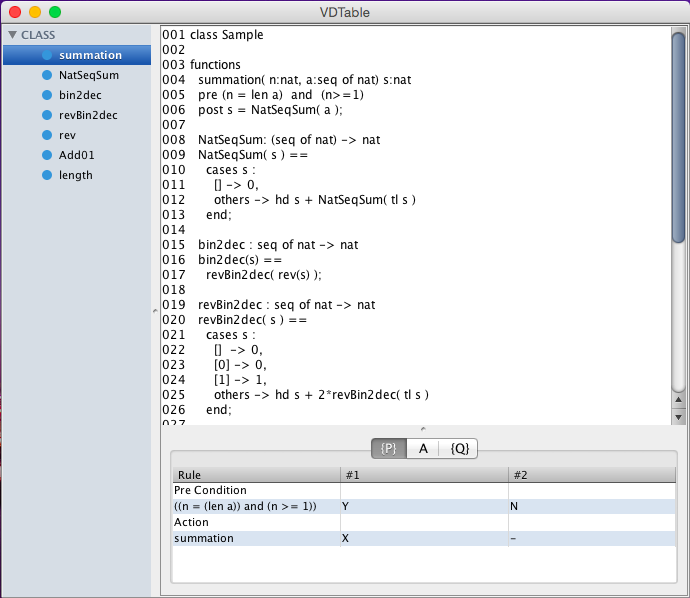

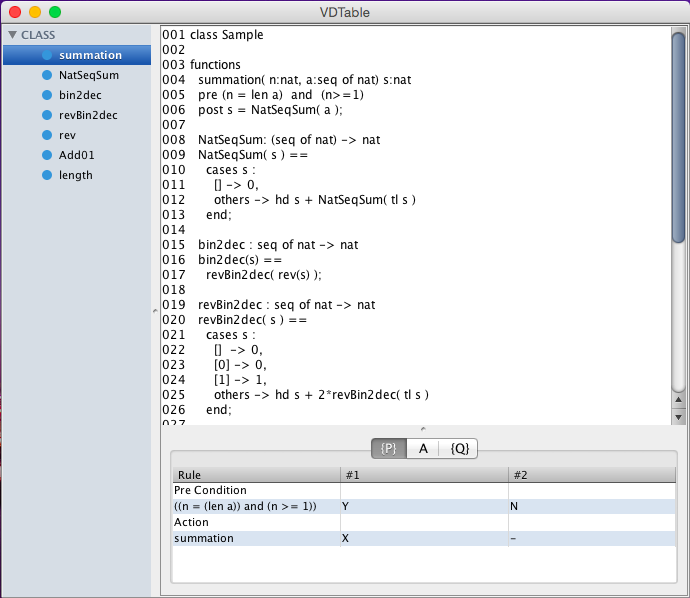

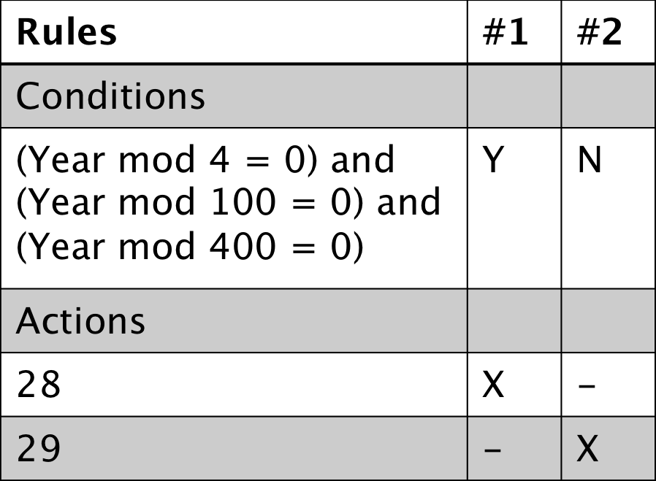

VDTableの外観

VDTableの外観

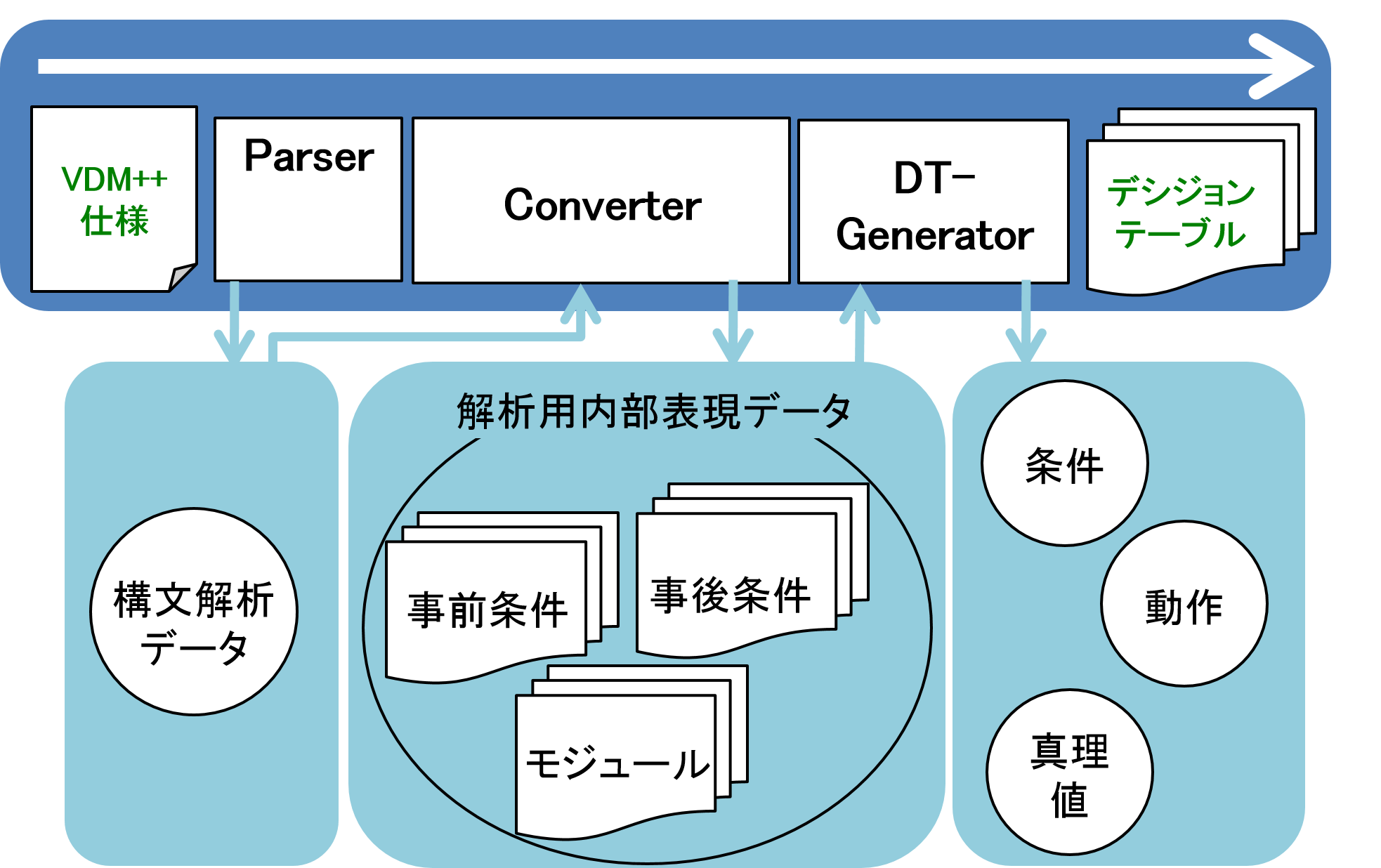

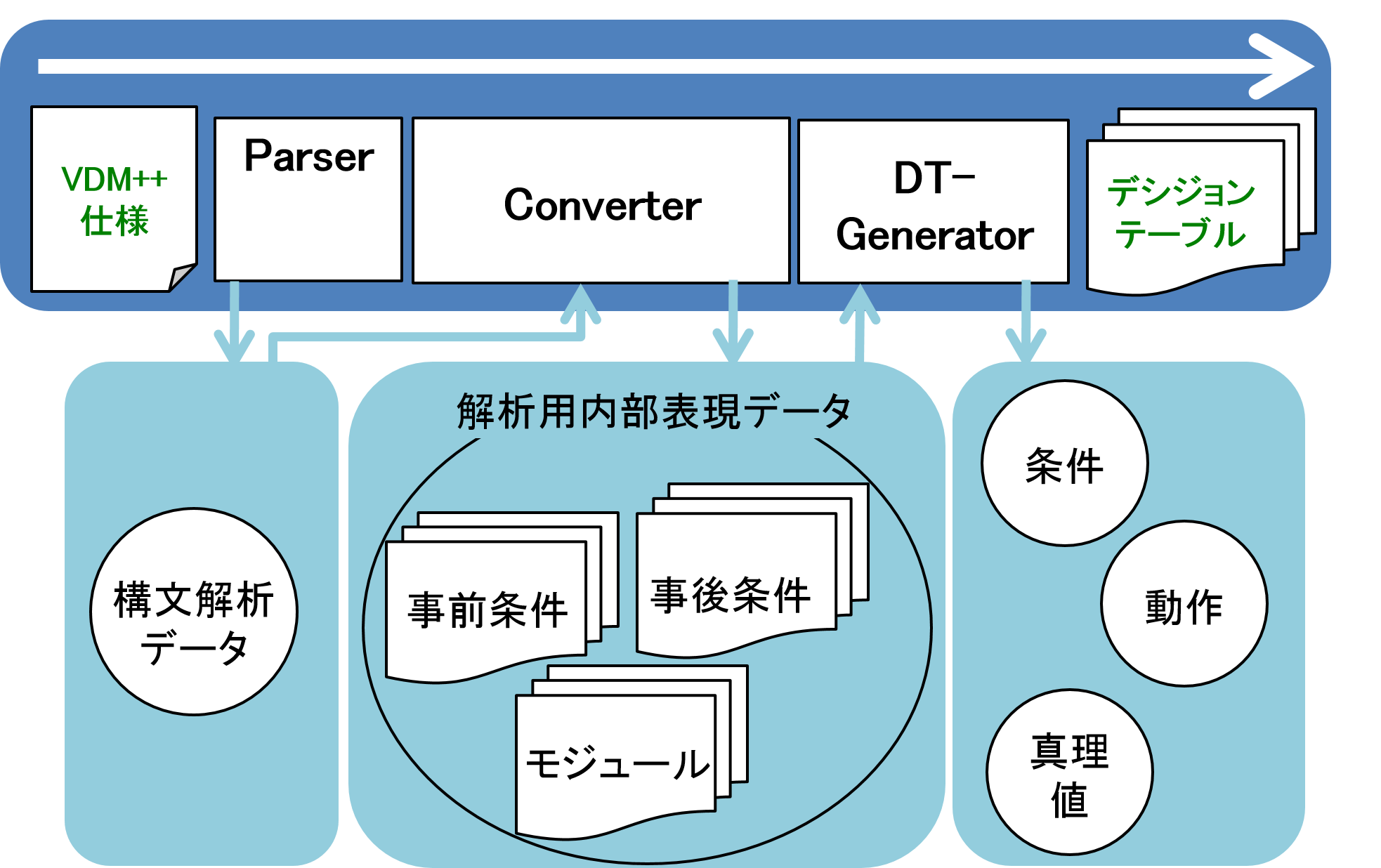

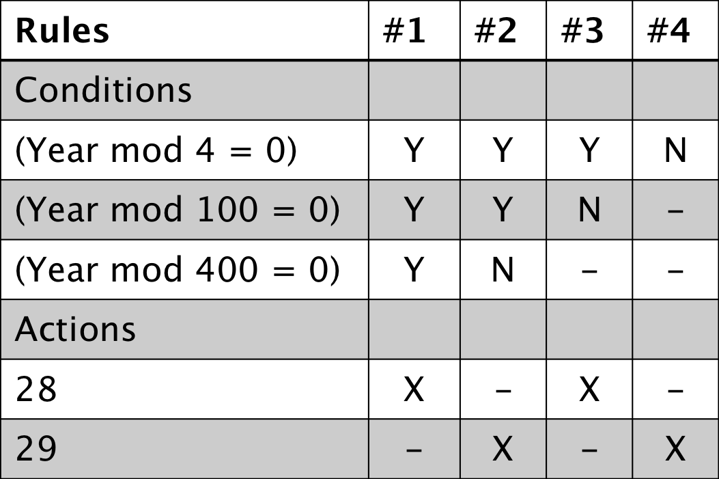

VDTable処理の流れ

VDTable処理の流れ

システムの大規模化、高性能化に伴い、従来の開発手法では、ソフトウェアの品質を維持できなくなってきている。同時に、重要なソフトに問題が起ると、大きな社会問題となる。

このような背景から、ソフトウェアの品質がより重要視されるようになった。

仕様書や設計書を、数理論理学を基盤とした仕様記述のための専用言語(形式仕様記述言語)を用いて厳密に記述したら、曖昧さや思い込みを開発プロセスの早期に排除し、手戻りによるコストを防ぐシステムの満たす性質について科学的、系統的な分析、品質を高めることができる。

形式手法の1つにVDM(Vienna Development Method)、及びその形式仕様記述言語としてVDM-SLがある。

一方、ソフトウェア開発の上流工程における設計検討段階では、ソフトウェアの論理を正確に表現する技法の1つに、デシジョンテーブルがある。

この技法は、ソフトウェアの設計段階や仕様整理、テスト設計において利用可能である。

西川氏が形式手法を用いたテスト設計時の作業効率化を目的として、

VDM++仕様を用いたデシジョンテーブル自動生成ツールVDTable(VDM Decision Table)を開発した。

入力:VDM++仕様

出力:デシションテーブル

VDTableの外観

VDTableの外観

VDTable処理の流れ

VDTable処理の流れ

VDM++仕様を用いたデシジョンテーブル自動生成ツールVDTable の実用性を高めること。

具体的には、複合条件式への対応をする。

生成したの現状

生成したの現状

予定の生成した結果

予定の生成した結果

問い合わせ先:hm12056@student.miyazaki-u.ac.jp

本ページ更新時間:2017/02/28

更新者:黄一諾